II dio Mikroprocesor

2.13. Superskalarni procesori

2.13.4. Tehnike izvršavanja instrukcija

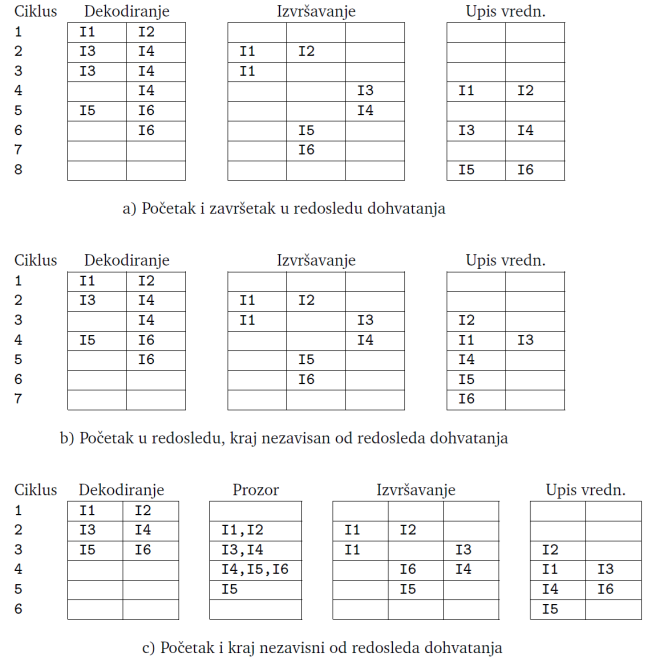

Prema izvedenim promjenama, instrukcije superskalarnih procesora se mogu podijeliti u tri grupe prema redoslijedu u kome počinje i završava obrada instrukcija:

1. Početak i završetak obrade instrukcija su u redoslijedu dohvatanja.

2. Početak obrade instrukcija je redoslijedu dohvatanja, dok je završetak u redoslijedu nezavisnom od redoslijeda dohvatanja.

3. Početak i kraj obrade instrukcija su u redoslijedu nezavisnom od redoslijeda dohvatanja.

Pri tome se mogu, u zavisnosti od dostignutog nivoa paralelizma instrukcija, u nekim instrukcijama promijeniti nazivi registara.

Primjer: na slici 23. je dat uporedni prikaz različitih tehnika za izvršenje niza od šest instrukcija za koje važi:

1. instrukcija I1 zahtijeva za izvršavanje dva ciklusa časovnika, sve ostale instrukcije zahtijevaju jedan ciklus,

2. instrukcija I1 radi sa brojevima u pokretnom zarezu, tj. zahtijeva za izvršavanje FPU,

3. instrukcije I2, I5 i I6 zahtijevaju za izvršavanje jedinicu FXUint ,

4. instrukcije I3, I4 zahtijevaju za izvršavanje jedinicu FXUBCD,

5. rezultati instrukcije I4 su argumenti instrukcije I5.

Svojstva obrade instrukcija su:

• vod može istovremeno da dohvati i dekodira dve instrukcije;

• procesor posjeduje tri razdvojene jedinice za obradu (npr. dve FX ALU – jednu za rad sa cijelim a drugu sa BCD brojevima i jednu FP ALU);

• vod instrukcija posjeduje dve instance pomoću kojih može istovremeno da predaje rezultate obrade.

Slika 23: Tehnike obrade instrukcija superskalarnih procesora

Ograničenja pri obradi < Index > Početak i završetak obrade instrukcija su u redoslijedu dohvatanja

|

|

|

|

|

|